掃碼添加微信����,獲取更多半導(dǎo)體相關(guān)資料

本文我們展示了一個使用純濕法方法的清潔過程的性能,光刻膠和側(cè)壁聚合物的去除是通過結(jié)合浸泡和使用環(huán)?�;瘜W(xué)方法的高壓噴霧工藝來完成的��,這減少了流程步驟的總數(shù)�,從而降低了總體成本,先前的工作表明���,物理分析�����,包括SEM��、EDX和Auger,以及電氣測試����,都需要確定清潔度�����,本研究的重點是電氣測試�,以確定僅濕清潔的性能�。

通過硅通(TSV)技術(shù)允許通過芯片垂直進(jìn)行電氣連接,當(dāng)集成到設(shè)計中時�,該技術(shù)可用于減少互連長度,減少軟件包的大小���,并增加芯片之間的帶寬���。在博世DRIE蝕刻過程中,這是通過交替進(jìn)行的腐蝕性蝕刻步驟和含氟聚合物沉積來完成的�,各種清潔的工藝被用來從TSV中去除這種聚合物材料,我們展示了一個使用獨家濕式方法的新濕式清潔過程的性能�����,使用電氣測試進(jìn)行性能評估����,并使用物理計量學(xué)進(jìn)行驗證����。

每個晶片在精確控制的條件下浸泡在加熱���、循環(huán)��、溶劑浸沒浴中�����,測序基于下游工藝時間�,確保芯片浸泡時間相同,通過適當(dāng)?shù)幕瘜W(xué)性質(zhì),浸泡時間允許光刻膠的溶解和去除側(cè)壁聚合物涂層�����,浸泡后,溶劑濕晶片被運送到一個單晶片自旋工藝站�,以完全去除殘留的光刻膠和側(cè)壁聚合物,高壓化學(xué)風(fēng)扇噴霧的使用增強了殘差的去除�。沖洗過程確保了晶片的完全清潔和無顆粒。

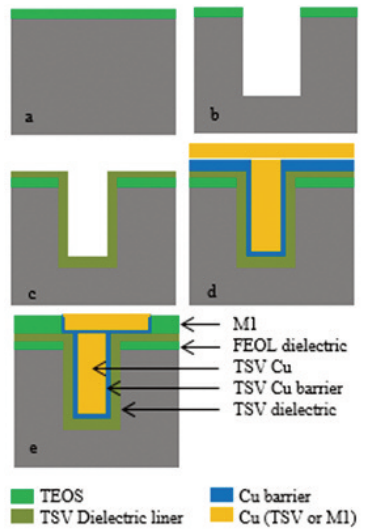

工藝流程如圖2所示���。正硅酸四乙酯(TEOS)薄膜首先沉積在(a)�����,蝕刻TSV與由臭氧/TEOS熱化學(xué)氣相沉積過程(c)�,形成的氧化物排列銅屏障和種子膜被沉積��,銅被電鍍到TSV(d)�,中使用CMP去除TSV-Cu覆蓋層,并在TSV(e)上方形成單一大馬士革金屬�。

?

圖2

實驗設(shè)計采用新的Veeco濕清潔代替現(xiàn)有的dHF/nh4OH:h2o2濕清潔,并代替灰和現(xiàn)有的濕清潔����,去除灰分步驟可將RIE處理時間減少33%。POR是有記錄的過程��。用電氣測試來評價清潔過程的性能��,顯示了測試設(shè)置的示意圖����。我們測量低壓下基底的泄漏電流,然后以階梯式斜坡電壓���,以找到TSV介質(zhì)斷裂的電壓�����,在我們的標(biāo)準(zhǔn)配置中�����,正電壓施加于CuTSV����,我們使用光學(xué)照明產(chǎn)生少數(shù)載流子,并增加一個延遲����,允許tsv氧化物硅電容器為充電。

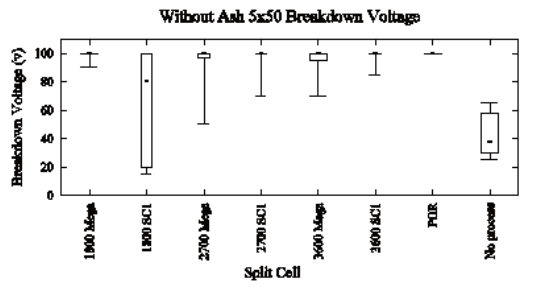

使用表中的配方表對5x50tev處理的步驟進(jìn)行清洗����。研究了三種不同的浸泡時間,每次進(jìn)行兩種沖洗過程����,變化總共運行了三次,此外�,使用我們的POR并行處理五片晶���,在沒有濕清潔的情況下處理兩片,圖2顯示了在5v時從tsv到晶片背面的泄漏電流����,每個分裂的細(xì)胞使用條形和胡須圖顯示,在每個晶圓上測量了32個直徑�,用于分裂細(xì)胞的所有晶圓都被結(jié)合在棒狀體和晶須中����。

沒有濕清洗的分裂細(xì)胞與使用我們的標(biāo)準(zhǔn)SC1和高頻清洗的晶片類似,這表明TSVis中的聚合物主要通過灰分過程去除����,與標(biāo)準(zhǔn)工藝晶圓相比,在Veeco清洗過的晶圓均顯示有泄漏電流的微小增加�����,浸泡時間和沖洗過程不影響可重復(fù)方式的泄漏電流測量��。

?

圖5

擊解波電壓如圖5所示,PORsplit電池中所有死亡設(shè)備的故障電壓均大于100v,所有沒有清潔工藝的模具都在60v前失敗了,在Veeco清洗的薄片有一些模具在100v以下出現(xiàn)故障�����,隨著清潔時間的增加,有更好的性能的趨勢����。在Veeco清洗過的晶圓的性能稍好,這表明有一些材料需要去除����。在Veeco清洗的晶圓與POR晶圓有相似的泄漏,外圍模具具有較低的測量電流,浸泡時間對泄漏電流的影響不大,無灰點2x40的故障電壓,隨著清潔時間的增加�����,外圍模具顯示出性能更好的趨勢��。

電氣和物理分析表明���,Veeco濕清潔可以從tsv中去除光刻膠和側(cè)壁聚合物殘留物�����。Veeco濕清洗過程已經(jīng)證明了基于泄漏電流和介電擊穿電壓與POR相似的結(jié)果���,同時消除了灰分,這是等離子體過程的重要組成部分��。數(shù)據(jù)中的額外擴展代表了大晶圓間和晶圓內(nèi)的變化,這可能是由于演示工具的手動特性以及從演示站點發(fā)運和返回晶圓所需的額外時間����。總的來說���,Veeco濕清潔工藝顯示了等效電氣結(jié)果��,通過消除等離子體灰降低了成本����。