掃碼添加微信,獲取更多半導體相關資料

在氫氧化銨溶液中��,使用各向異性硅蝕刻技術�����,在SOI晶片上制備了無連結fet(JL-FET)器件���,以O2/N2電子回旋共振(ECR)等離子體作為柵極介質(zhì)生長氮氧化硅����,以反應性濺射作為柵極金屬沉積硝化鈦�����,利用掃描電鏡成像和電學測量方法對其結構進行了表征���,最終得到的硅通道厚度為65nm�,器件的電性能與預期一致�����。

通常在幾納米內(nèi)從1020個原子/cm3p型摻雜劑到1020個原子/cm3n型摻雜劑����,相比之下,JLFET器件在整個器件中具有相同的摻雜濃度���,從而降低了摻雜劑的擴散速率��,除了使用標準的熱退火和更少的離子注入步驟可以降低制造成本外�,JL-FET也因其性能而脫穎而出,電流密度通過襯底[1]的厚度分布����,參與電流的載流子為大多數(shù)類型,并且一些電荷散射現(xiàn)象可以通過極化柵在平帶條件來減輕����,這允許給定器件的更大電流。

在高頻緩沖溶液中�����,使用濕式氧化和氧化硅蝕刻法將襯底變薄到約200nm�,然后將晶片在50keV下離子注入磷,劑量為1013個原子/cm2���,摻雜劑活化在1000°C的常規(guī)烤箱中惰性氣體中進行30分鐘����,這一離子注入步驟的計劃比通常劑量低�����,因為較低濃度的摻雜雜質(zhì)會導致更寬的耗盡區(qū)域���,通過犧牲一些電接觸質(zhì)量�����,在模擬步驟中只在25nm中觀察到的晶體管行為���,以及在更薄的器件中,即使在75nm厚的器件上也可以觀察到����,通過光刻技術確定了活性區(qū)域。

通過ECR等離子體培養(yǎng)氧化硅硬掩模�����,并在HF緩沖溶液中蝕刻�,然后在氫氧化銨溶液中進行各向異性硅蝕刻,持續(xù)40秒�����,采用掃描電鏡成像技術證實了濕式蝕刻過程���,柵極氧化物是通過o2/n2ECR等離子體生長的氮氧化硅�,柵金屬由光刻和升降機定義,由濺射氮化鈦制成��,用光刻法和高頻溶液蝕刻法對覆蓋漏極和源區(qū)的氧化物進行蝕刻����,用濺射法沉積金屬墊片,最終退火分5分鐘進行�����,在450°C的常規(guī)烘爐上形成氣體(H2)�。

?

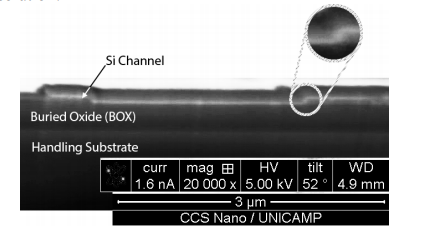

每個退火步驟后,在Keithley證明上測量裝置I-V曲線�����,通過退火和電測量����,使用Ga+聚焦離子束磨削和掃描電鏡成像提取橫截面圖像,圖1清楚地顯示了預期的幾何結構���,使用圖像編輯所進行的測量�,軟件結果表明,氫氧化銨溶液濕蝕刻后的通道厚度約為65nm����,通道壁在(100)和(111)晶體平面之間的特征角約為57度,圓形邊緣是在各向異性蝕刻過程中出現(xiàn)的元穩(wěn)定(311)平面的結果�,這些結果表明,在氫氧化銨溶液中使用硅濕蝕刻確實可以令人滿意地減薄通道厚度�。

?

?

圖1

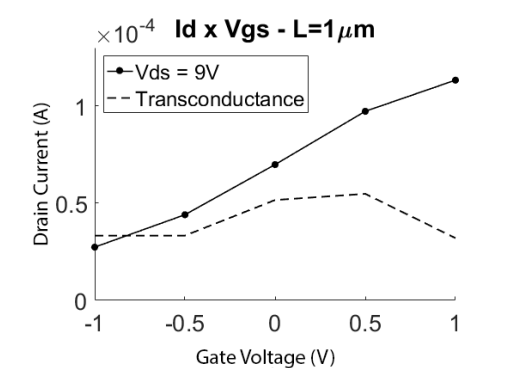

每個退火步驟后進行的電測量取得了不同程度的成功,顯示最佳接觸質(zhì)量和晶體管行為的測量是退火20分鐘后的測量��,與預期的那樣���,大多數(shù)測量結果顯示柵極電壓對電流的影響減弱,如圖所示2���,這是因為在65nm通道厚度時�����,由柵極引起的耗盡區(qū)域不夠?qū)?�,不足以耗盡每個載流子�,器件的閾值電壓變得非常負�����,并且器件在大多數(shù)VDS范圍內(nèi)作為門控電阻。在電觸點質(zhì)量較低��,像肖特基二極管�����,扭曲了I-V測量���,這是因為大約1017個原子/cm3的最終摻雜濃度在源和漏極區(qū)域不夠高��,無法保持歐姆接觸��。

?

圖2

盡管由于其負閾值電壓而不能作為開關����,但IDxVDS結果表明發(fā)生了晶體管行為和低柵極漏電流��,所制備的器件具有明確的三極管和飽和區(qū)域的晶體管行為����,但不能實現(xiàn)截止。對氫氧化銨濕式蝕刻過程的進一步調(diào)整可能導致JL-FET設備的電氣性能可與最先進的增強型MOSFET設備相媲美�,因此����,本研究證明了氫氧化銨溶液中的各向異性硅刻蝕是一種制薄硅基JL-FET器件通道襯底的可行技術���。