掃碼添加微信���,獲取更多半導(dǎo)體相關(guān)資料

本文章介紹了一種深垂直晶片孔和銅金屬化射頻硅集成的新方法�,通過晶片孔通過深干蝕刻工藝實(shí)現(xiàn)��,并使用銅電鍍填充����;提出了一種填充干蝕刻�、高高寬比、緊密間隔間隙的新技術(shù)��,并介紹了通晶片銅插頭的制備工藝和電學(xué)表征��,利用該技術(shù)���,成功地實(shí)現(xiàn)了幾種具有通晶片連接的新型射頻結(jié)構(gòu)�����。

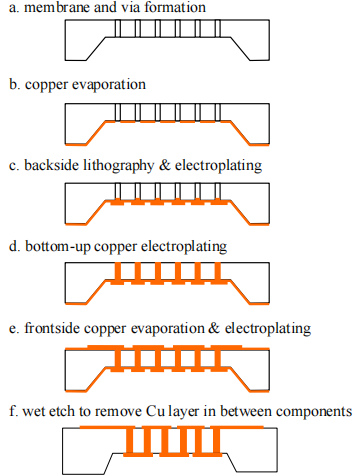

實(shí)現(xiàn)三維射頻組件的工藝流程如圖1所示����,在這些實(shí)驗(yàn)中使用了標(biāo)準(zhǔn)的4英寸<100>硅片�,采用各向異性濕蝕刻步驟����,局部將晶片厚度降低至目標(biāo)值(到晶片正面的期望距離地平面)��,在我們的實(shí)驗(yàn)中��,使用了25-150μm厚的硅膜����,通過膜的電感耦合等離子體蝕刻,實(shí)現(xiàn)了方形和圓形的高縱橫比通孔�,通過PECVD或LPCVD在孔的兩側(cè)或孔內(nèi)沉積一個(gè)氧化物隔離層,在晶片的背面蒸發(fā)了20nm的Cr粘附層和300nm的Cu種子層�,這種蒸發(fā)過程具有方便的特點(diǎn),蒸發(fā)的金屬不能深入內(nèi)部��。

?

?

圖1

因此�,銅島在通道的底部附近形成,并迅速生長����,這導(dǎo)致了通道底部的部分堵塞,這對(duì)于下一步的自下而上的電鍍是非常理想的�,采用光刻法確定這一側(cè)的金屬結(jié)構(gòu),并進(jìn)行銅電鍍����,以增加這些結(jié)構(gòu)的金屬厚度��,在這一步中�,隨著銅從內(nèi)部的銅種子生長���,通道的底部完全堵塞��。

一旦達(dá)到晶片背面Cu結(jié)構(gòu)的期望厚度��,在這一側(cè)施加光刻膠層���,同時(shí)進(jìn)行自底而上的銅電鍍�����,直到孔完全填充����,得到均勻的通晶片銅塞,然后在晶片的正面進(jìn)行另一次銅蒸發(fā)����,然后進(jìn)行光刻和電鍍�����,以實(shí)現(xiàn)這一側(cè)的射頻結(jié)構(gòu)���,然后去除樹脂,并執(zhí)行濕蝕刻步驟�����,將蒸發(fā)的銅剝離在射頻結(jié)構(gòu)之間�,這樣就實(shí)現(xiàn)了三維銅射頻組件。

?

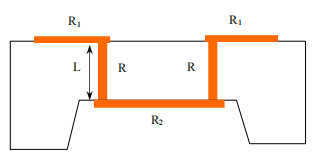

圖5

為了評(píng)估杯塞的電性能����,在設(shè)計(jì)和評(píng)估中包括了幾種測(cè)試結(jié)構(gòu),一個(gè)電阻/阻抗測(cè)量結(jié)構(gòu)的示意圖如圖5所示���。該結(jié)構(gòu)包括兩個(gè)直徑為40μm��,長度為L(電阻=R)��,兩個(gè)接觸墊(R1)和底部電阻(R2)�����,這種結(jié)構(gòu)是在不同膜厚度(或不同L)的不同晶片上實(shí)現(xiàn)的��。

利用電感耦合等離子體技術(shù)的透晶片蝕刻工藝已被用于通過膜的形成���,不同形狀和不同直徑(5~50μm)的氣孔已成功蝕刻�����,對(duì)于相同形狀和尺寸的孔陣列�����,蝕刻參數(shù)在晶片上具有高度的各向異性分布和較大的均勻性���,如果要一次蝕刻不同尺寸的氣孔��,則需要對(duì)工藝進(jìn)行更多的調(diào)整�。較大的蝕刻的更快,側(cè)壁可能會(huì)變細(xì)��。

對(duì)電阻結(jié)構(gòu)進(jìn)行了測(cè)量�����,并提取了電阻,孔內(nèi)的平均銅電阻率為2.5x10-5Ωcm����,與通常通過填充使用的摻雜多晶硅(大于10-2Ωcm)相比,這些銅填充孔的電阻率極低�����,這是非常有吸引力的����,特別是需要非常高密度的應(yīng)用,因此低電阻率是至關(guān)重要的����。

綜上所述,提出的一種新的透晶片銅電鍍技術(shù)�����,這種銅插形成技術(shù)可以實(shí)現(xiàn)更高的集成密度和更好的射頻器件���,此外�,后處理方法保持了與傳統(tǒng)集成電路過程的兼容性,有利于在硅中進(jìn)行無源組件和有源電路的集成���,利用我們的技術(shù)實(shí)現(xiàn)了透晶片銅插頭和新型的地下電感器����、傳輸線��、串?dāng)_隔離結(jié)構(gòu)等射頻結(jié)構(gòu)�,從而證明了該方法的潛力,通過電阻率得到的結(jié)果非常低����,這使得該方法也非常適合于高密度的互連。