掃碼添加微信,獲取更多半導(dǎo)體相關(guān)資料

引言

在硅襯底上制造電子芯片或集成電路需要大量的基本操作���,例如離子注入�, 本研究將涉及光刻��,介質(zhì)和金屬薄層沉積�����,機械化學(xué)拋光��,熱處理(退火或氧化)和“濕”處理。

表面準(zhǔn)備和清潔是這項技術(shù)的一個有點吃力不討好的方面���,因為它們是“看不見的”: 它們包括去除污染物和控制界面�����,然而���,在需要處理的層是納米級的時候,我們注意到與這些方面有關(guān)的研究變得至關(guān)重要��,并對“專門知識”作出了重大貢獻��,而“專門知識”有時很難得到重視�����。

一些選擇性蝕刻是通過濕法(在溶液中)進行的�����,具有很高的精度��,厚度變化從幾埃到幾微米���。 “表面準(zhǔn)備”處理允許 本備忘錄中討論的兩個主題更具體地涉及集成電路互連電平的清潔: 首先��,將介紹低或極低介電常數(shù)介電材料在清潔溶液中的行為研究�����。 特別是�,我們研究了這些材料的穩(wěn)定性或溶解性�,以及液相中的污染現(xiàn)象(胺,有機化合物和來自清潔溶液的表面活性劑的吸附)�����,這些現(xiàn)象導(dǎo)致電介質(zhì)的相對介電常數(shù)的不期望的變化���。 研究了它們的孔隙率隨清潔處理(含氫氟酸的溶液)中使用的等離子體處理的變化���。 在這一部分中使用的實驗技術(shù)主要是橢圓偏振法,橢圓孔隙率法��,紅外光譜法(透射法��,全衰減法和多重反射法)�,X射線反射法����,TOF SIMS以及接觸角和允許性測量���。

?

性能競賽

在微電子領(lǐng)域�,金屬氧化物半導(dǎo)體(CMOS)類型的硅襯底上的集成電路的技術(shù)發(fā)展被描述為“Neud technologique”�����,該“Neud technologique”對應(yīng)于所制造的最小晶體管的柵極尺寸�。 因此,提高集成電路性能的兩個主要研究因素是晶體管的開關(guān)速度���, 另一方面��,電路功能的增加與電路中集成的晶體管數(shù)量的增加有關(guān)�。 性能競賽導(dǎo)致了電路小型化競賽�,由一個由工業(yè)和學(xué)術(shù)專家組成的國際委員會制定的規(guī)范嚴(yán)格控制,并以國際半導(dǎo)體技術(shù)路線圖(ITRS)的名義公布�。 這些規(guī)范定期審查和更新,以考慮到 真正的進步和仍然存在的困難�。

同時,硅襯底尺寸從4英寸逐漸增大到12英寸(300mm)���,使該工藝在很大程度上有利可圖����,每片可實現(xiàn)多達200個芯片��,并說明了在硅錠生長中獲得的控制���。 然而��,由于不同尺寸的基材的生產(chǎn)設(shè)備的發(fā)展����,也出現(xiàn)了新的技術(shù)和工業(yè)問題�。

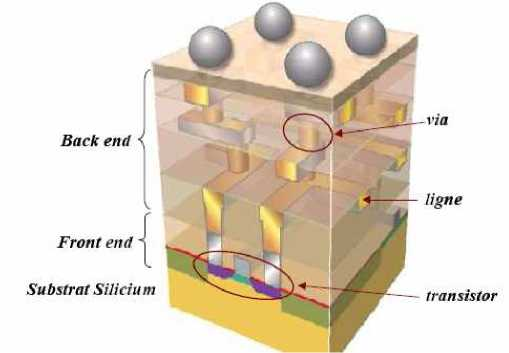

簡單地說,集成電路由兩個主要部分組成(圖1): 有源部分����,也稱為線前端(FEOL),對于在硅襯底中制造的晶體管�����。 互連級��,或BEOL,用于將晶體管連接在一起���。 它們由金屬線組成���,通過圓柱形“通孔”相互連接,并嵌入絕緣材料中�。 今天達到的晶體管密度需要能夠使連接它們的線交叉,這導(dǎo)致互連水平成倍增加�。 例如,為65nm技術(shù)制造了7個金屬能級��。

?

圖1電路集成的表示方案

除了晶體管和互連線之外���,還可以在FEOL部分或BEOL部分中找到諸如板載電容之類的元件���,這取決于技術(shù)NUD。 此外�����,最近直接在硅襯底上的圖像傳感器的發(fā)展現(xiàn)在導(dǎo)致了系統(tǒng)的復(fù)雜性�����,以便在晶體管處集成光電二極管,在最后的鋁BEOL互連處集成濾色器和微透鏡��,或者在襯底的背面上集成光電二極管���。

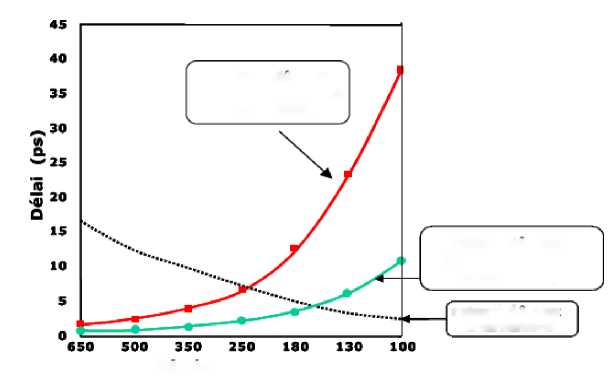

互連水平:不同技術(shù)節(jié)點規(guī)格的演變,有兩個主要因素有助于電路的響應(yīng)時間�����,晶體管的開關(guān)時間和信號在互連中的傳播時間��。

隨著晶體管和互連網(wǎng)絡(luò)的臨界尺寸的減小���,對于使用鋁作為金屬和使用氧化硅作為金屬間絕緣體的技術(shù)�,這兩種貢獻的相對重要性從Neud 250nm開始反轉(zhuǎn)(圖2)����,這是因為尺寸的減小而且彼此越來越接近促進了兩個相鄰線路之間的電容耦合。因此�,減小與互連中的信號傳播相關(guān)的延遲迅速成為一個突出的問題。 在一階上�����,它取決于構(gòu)成導(dǎo)電線的金屬的電阻率和線間絕緣體的相對介電常數(shù)(或介電常數(shù)),銅和低介電常數(shù)(Low-K)電介質(zhì)從120納米技術(shù)NUD中被引入�����,以取代鋁和SiO2��。

?

結(jié)論和展望

整個工作證明了SiOCH型低介電常數(shù)介電材料在氣相中和在液相中與非極性有機分子和表面活性劑的高親和力�����。 從實際的角度來看����,這導(dǎo)致了整合方案的修改,并將清潔化學(xué)物質(zhì)的選擇導(dǎo)向水溶液�����,該水溶液主要由稀釋的有機酸組成�,作為基于稀釋的HF的方法的補充,該方法可以保存到Neud 40nm�。

關(guān)于多孔介質(zhì),我們進一步證明: 在等離子體蝕刻處理之后�,在材料的表面上形成更致密的5nm至10nm的層,具有減少的孔隙率,然而��,該層對氣體擴散不是密封的�����。 根據(jù)所使用的不同探針分子�,該層的選擇性在一階上與氣體和固體之間的極性相互作用有關(guān),而不是與分子的尺寸有關(guān)清潔處理和硅烷化類型的最終表面功能化�����。

蝕刻后清洗的挑戰(zhàn):蝕刻殘留物的特性

在實現(xiàn)集成電路互連水平時�����,最關(guān)鍵的清潔是那些底層的銅暴露在所使用的化學(xué)物質(zhì)中的清潔工作�����。(2)在實現(xiàn)集成電路互連水平時����,最關(guān)鍵的清潔工作是那些底層的銅暴露在所使用的化學(xué)物質(zhì)中的清潔工作是那些底層的銅暴露在所使用的化學(xué)物質(zhì)中的清潔工作�。 實際上,金屬的任何過度腐蝕都可能導(dǎo)致器件的電性能和可靠性的嚴(yán)重退化。 例如��,在“鳥嘴”型缺陷的情況下(圖27)�,由于銅的溶解而在電介質(zhì)下方產(chǎn)生的真空將導(dǎo)致可靠性問題。

首先����,通過俄歇效應(yīng)XPS和TOF SIMS光譜分析蝕刻O3圖案后留在銅表面的殘留物(圖28),先前的研究[31��,32���,3]表明����,在使用氟碳等離子體蝕刻電介質(zhì)后�����,在圖案的側(cè)面上留下的殘留物主要由CFx(x=1-3)����,CH,Co鍵組成�,并含有等離子體濺射銅����。 在銅上檢測到CuFx物種�。 與這項工作相一致的是,我們對大面積銅進行的分析表明��,碳���,氟和氧含量很高�,特別是XPS證實了CuO型氧化銅層的形成���。

在清洗過程中去除這些殘留物對于確保兩個金屬層之間的良好導(dǎo)電是必不可少的����。 由于它們的性質(zhì)����,很難知道它們是否可以直接溶解在清潔溶液中���,或者它們是否可以通過溶解氧化銅和可能的輕微蝕刻銅來去除��,這有助于它們的脫落�。對銅的腐蝕和氧化銅在清洗液中的溶解感興趣是非常重要的。 將特別注意通過限制金屬銅的溶解來快速溶解氧化物���。