掃碼添加微信,獲取更多半導(dǎo)體相關(guān)資料

引言

本文主要報道了ProTEK PSB在實際應(yīng)用條件下的圖形化特性��、抗蝕性和去除特性�����。研究發(fā)現(xiàn)了ProTEK PSB的兩個問題:不可接受的大側(cè)刻和有機溶劑或氧化灰難以去除引物��。為了制造一個lsi集成的觸覺傳感器���,我們使用了帶有低溫氧化物底層的ProTEK PSB���。這種組合解決了ProTEK PSB的側(cè)面刻蝕問題和低溫氧化物的針孔問題,提供了可以在低溫下制備的實用堿性刻蝕掩膜�。

?

實驗

首先,在Si基板上適量滴加底漆�����,在3000pm下旋轉(zhuǎn)涂布1分鐘��。 涂布底漆后����,使用熱板在110C下280°℃分鐘 用加熱1分鐘�����。 然后��,滴下ProTEKPSB���,與底漆相同����,在3000 rpm下旋涂1分鐘。 涂上ProTEK PSB后��,用熱板在110℃下加熱1分鐘加熱���。加熱后��,用I線以1000mJ/cm2的曝光量進行曝光�。 曝光后���,用熱板在110℃下加熱2分鐘���。 影時����,在乳酸乙酯中浸泡5分鐘����,充分攪拌, 顯影后����,用異丙醇( IPA )清洗,用旋轉(zhuǎn)干燥器干燥�。 最后,用熱板在220C下加熱3分鐘使之硬化��。

?

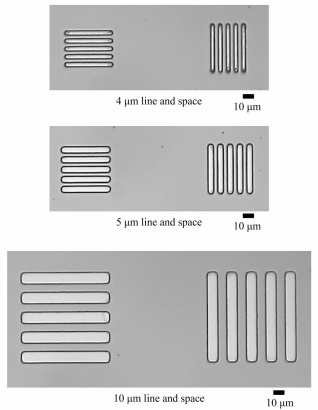

圖1

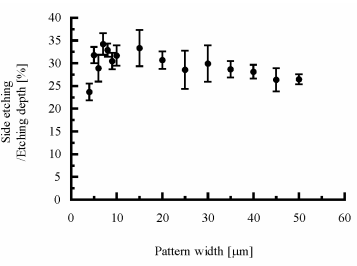

如圖1所示可以形成4μm����,5μm和10μm的線和空間,在這些臺階上測量的膜厚均為3μm���。 本研究使用表面形狀測量儀進行了膜厚測量��, 在圖案化后�,使用TMAH(25%��,80°C)蝕刻Si,相對于蝕刻深度5μm����,側(cè)蝕刻為1.5μm, 側(cè)蝕刻相對于蝕刻深度的比例(如圖2所示)����,與圖案寬度無關(guān),約為30%�。 這種側(cè)面蝕刻不是大多數(shù)應(yīng)用都能允許的量,需要改善光刻膠的附著力���。

?

圖2

對集成LSI和MEMS傳感器的觸覺傳感器的制作中應(yīng)用ProTEK PSB的例子進行說明。 使用ProTEK PSB的工序如圖4所示��,是將作為傳感器結(jié)構(gòu)體的Si晶圓和LSI晶圓用樹脂粘接后�,形成傳感器結(jié)構(gòu)體和導(dǎo)線取出槽的堿濕蝕刻工序。

由于LSI晶圓背面沒有附著氧化膜�,需要沉積用于堿性濕法蝕刻的掩膜材料。但是�����,由于LSI晶圓不能進行高溫工藝���,不能使用熱氧化膜和熱CVD的氮化膜����。另外,通過等離子CVD的低溫氧化膜/氮化膜和濺射沉積的金屬膜由于有針孔��,不適合作為掩膜�����。 因此����,在掩膜中使用了ProTEK PSB。 ProTEK PSB顯影后���,用IPA清洗���,用旋轉(zhuǎn)干燥器干燥。 最后����,使用熱板在220℃下加熱3分鐘使其硬化。 此時���,就會產(chǎn)生上述側(cè)面蝕刻的問題�����。 這可能是因為本裝置使用的是粘著劑��,因此清洗受到限制��,僅使用2.5%氨水進行清洗�����。 因此使用等離子體CVD的低溫氧化膜和ProTEK PSB的組合����,或者濺射的低溫氧化膜和ProTEK PSB的組合����。

作為能夠低溫形成的堿性濕法蝕刻用掩模,與單獨使用低溫氧化膜和ProTEK PSB的掩模相比�,低溫氧化膜和ProTEK PSB組合的掩模能夠抑制側(cè)面蝕刻,為了更容易理解而進行的比較實驗的結(jié)果���。 作為掩膜��,顯示了使用(a)ProTEK PSB���、(b)通過等離子CVD堆積的低溫氧化膜�����、(c)通過等離子CVD堆積的低溫氧化膜和ProTEK PSB的組合����、以及(d)通過高頻磁控濺射堆積的低溫氧化膜和ProTEK PSB的組合的結(jié)果�。 這里,蝕刻深度為200μm����。 僅將低溫氧化膜用于掩模時,針孔不僅會產(chǎn)生蝕刻坑����,特別是在掩模端通過針孔進行側(cè)面蝕刻。 另一方面����,如果將低溫氧化膜與ProTEK組合,則可以得到良好的結(jié)果。

?

結(jié)論

對新型堿性濕法蝕刻用負型光敏性抗蝕劑ProTEK PSB和非光敏性的ProTEK B3進行了評價���。 使用ProTEK PSB可以形成4μm的線和空間���。 另外,側(cè)面蝕刻相對于蝕刻深度的比例約為30%����,與蝕刻寬度無關(guān)。 另外����,ProTEK PSB可以用O2灰化除去,殘留的底漆可以用1%HF完全除去���。 側(cè)面蝕刻較大�����,以及底漆剝離需要HF,這是ProTEK PSB實際應(yīng)用于器件時的問題����。 本論文提出了回避這些問題的方法。

將涂有ProTEK B3的Si基板在TMAH(25%,80°C)中浸泡24小時后��,通過側(cè)面蝕刻從晶圓端剝離了1 mm��。 另外��,ProTEK B3可以用丙酮和O2灰化除去�����,殘留的引物可以用1%HF完全除去���,將LSI和MEMS傳感器集成化的觸覺傳感器的制作工藝適用于ProTEK PSB����。 在從LSI晶圓背面取出器件的電線的工序中�,通過TMAH對LSI晶圓背面進行蝕刻,但由于工藝溫度的限制���,無法在LSI晶圓上形成熱氧化膜和高溫氮化膜作為掩模材料�����。

因此�����,在利用等離子CVD在350°C下沉積���,或者利用高頻磁控濺射沉積的低溫氧化膜上對ProTEK PSB進行圖案化��,利用HF對低溫氧化膜進行蝕刻����,直接利用TMAH進行了蝕刻�。 因此防止了低溫氧化膜從針孔中的蝕刻,如果使用通過等離子體CVD在350℃下沉積的低溫氧化膜�����,則側(cè)蝕刻可以控制在9μm���,如果使用通過高頻磁控濺射沉積的低溫氧化膜��,則側(cè)蝕刻可以控制在15μm�����。