掃碼添加微信�,獲取更多半導(dǎo)體相關(guān)資料

摘要

在硅晶片上制造集成電路涉及數(shù)百個(gè)單獨(dú)的工藝步驟�。在處理的早期階段,在將摻雜劑引入 Si 之前����,通常很少擔(dān)心 Si 從晶片表面通過氧化或蝕刻損失。與互補(bǔ)金屬氧化物半導(dǎo)體器件的有源區(qū)的 <1 微米厚度相比��,晶圓厚度通常 >600 微米����,對(duì)于所有實(shí)際用途而言幾乎是無限的。在利用輕摻雜外延層來提高器件性能的晶圓上�����,該層的典型厚度也相對(duì)較大�,為 5-10 mm。通常�,仔細(xì)控制各種清潔和氧化步驟對(duì)表面粗糙度的影響。通過化學(xué)清洗對(duì)硅去除的常規(guī)監(jiān)測(cè)并未廣泛進(jìn)行�。許多濕化學(xué)清洗方案用于制造�,其中最流行的是由 Kern 在 1965.1,2 開發(fā)的 RCA 標(biāo)準(zhǔn)清潔 (SC1) 這種清潔的主要目的是去除晶片上的雜質(zhì)���,例如顆粒和金屬表面�����。RCA clean 旨在通過兩個(gè)步驟完成此操作�����。

實(shí)驗(yàn)條件和結(jié)果

通過晶片鍵合形成的市售 SOI 晶片用于這些實(shí)驗(yàn)�。這些晶片是通過所謂的 SmartCut 工藝生產(chǎn)的���,其中在鍵合前適當(dāng)?shù)臍渥⑷胗兄谠谘趸?Si 襯底上形成薄 Si 膜��。 5 起始晶片由 2000 ? 單晶 Si 膜組成由 4000 ? 的熱 SiO2 與體硅襯底隔開���。基板和薄膜在 (100) 平面上取向�,名義上未摻雜,具有 14-22 W cm 的電阻率的輕度 p 型���。SOI 薄膜在 1000°C 下通過幾次犧牲干氧化變薄����,從最初的 2000 ? 厚度降至約 120 ?。在每個(gè)氧化步驟之后�,使用光譜反射法和/或單波長(zhǎng)橢圓偏振法繪制生長(zhǎng)氧化物和剩余 Si 的厚度����。

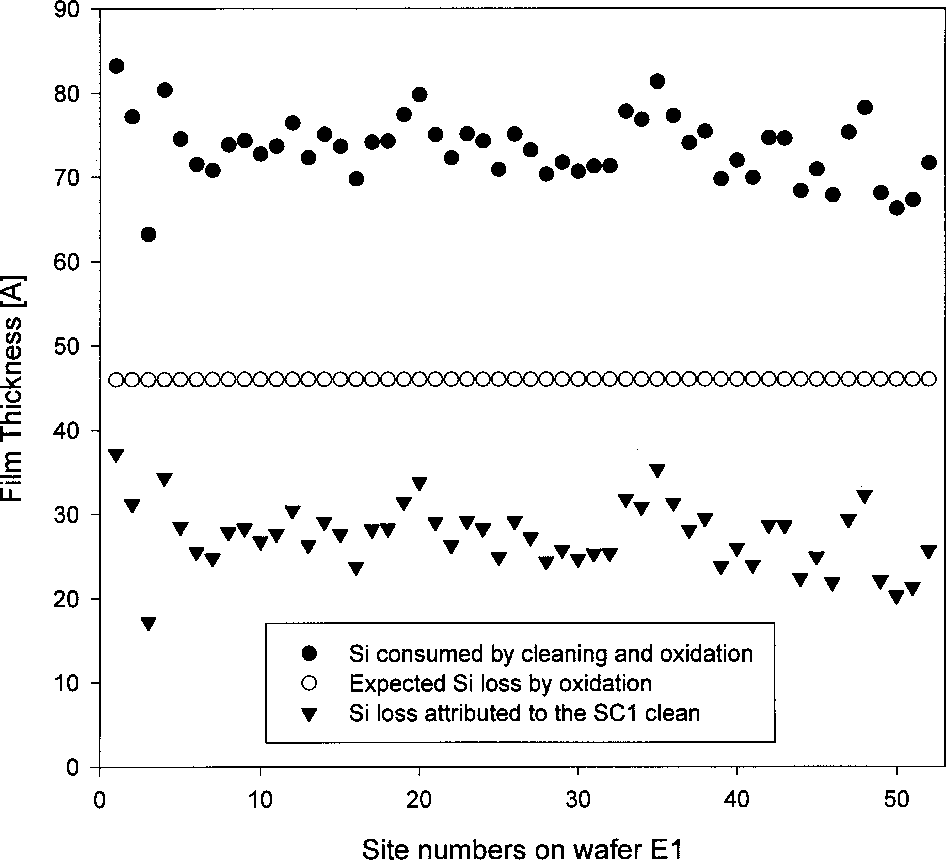

對(duì)于 Si 和氧化物厚度 >1000 ?,預(yù)測(cè)值和測(cè)量值之間的任何差異都在 2% 以下�,在三層結(jié)構(gòu)的實(shí)驗(yàn)精度范圍內(nèi)。(對(duì)于多層結(jié)構(gòu)�����,實(shí)驗(yàn)不確定性大于單個(gè)薄膜��。不僅所有薄膜的光學(xué)參數(shù) n 和 k 需要眾所周知��,而且實(shí)驗(yàn)擬合假設(shè)完全突然和光滑的界面����。)因此,對(duì)于較厚的薄膜��,很難測(cè)量由蝕刻引起的 Si 厚度的小損失���。當(dāng)平均厚度為 120 埃的 Si 膜在 850°C 的干氧中進(jìn)行清潔和氧化以獲得 100 埃的襯墊氧化物時(shí)�,很明顯發(fā)生了嚴(yán)重的 Si 損失。

1.?SOI 晶片的氧化率明顯高于體硅���,這是由于缺陷或由于薄 Si 膜中的應(yīng)力�����;

2.?SC1 清潔過程消耗了 25-30 ? 的硅��。

由于在熱氧化過程中 Si 填隙物被注入到 Si 中�,我們一直在觀察是否有任何跡象表明掩埋氧化物(它可以是填隙物的屏障或匯)通過其對(duì)填隙物濃度的影響來影響氧化速率����。在一系列氧化過程中,SOI 晶片上生長(zhǎng)了高達(dá) 3000 ? 的氧化物�����,體硅監(jiān)控晶片和 SOI 晶片之間從來沒有任何可測(cè)量的差異�����。在 100 ? 的 Si 上生長(zhǎng) 100 ? 的 SiO2 也導(dǎo)致了正確的 SiO2 厚度,但 Si 短缺 25-30 ?��。如果增強(qiáng)的氧化是造成 Si 損失的原因��,我們將獲得接近 160 ? 的 SiO2�����。

??

??

SC1溶液

由氫氧化銨 (NH4OH)��、過氧化氫 (H2O2) 和水組成�。H2O2 的主要目的是氧化硅��,然后在 NH4OH 的幫助下溶解氧化物�����。將 Si 浸入 SC1 會(huì)導(dǎo)致不超過 6 ? 的化學(xué)氧化層生長(zhǎng)���,此時(shí)達(dá)到穩(wěn)態(tài)條件����,即 Si 的氧化速率和氧化物的溶解速率相等��。 6,7 除非具體測(cè)量旨在檢測(cè)硅消耗量,通常不會(huì)觀察到硅的損失��。有三種方法可以測(cè)量去除的 Si 量:

部分掩蔽表面的輪廓分析���,4 (ii) 非常精確的晶圓稱重��,8 和 (iii) 相對(duì)于明確定義的深度標(biāo)記的厚度測(cè)量����。8 SOI 晶圓中的掩埋 Si/SiO2 界面提供了完美的標(biāo)記. 一個(gè)原子銳利的界面可以放置在離表面足夠近的位置���,以便去除的厚度占總距離的很大一部分����。

結(jié)論

SC1 清潔程序可去除有限量的硅�。

文章全部詳情,請(qǐng)加華林科納V了解:壹叁叁伍捌零陸肆叁叁叁