掃碼添加微信,獲取更多半導(dǎo)體相關(guān)資料

引言

? ? ? 半導(dǎo)體技術(shù)必須持續(xù)發(fā)展����,以増 加IC性能與功能,同時減小芯片尺 寸��,降低耗電量與成本?�,F(xiàn)在發(fā)展出具創(chuàng)新性�����、小尺寸�����、成本效益 之三維導(dǎo)線互連技術(shù),可滿足以上需求����。其中,技術(shù)由于采取三維互連方法��, 可加速晶片堆疊技術(shù)上之應(yīng)用�,尤其在異質(zhì)元件整合上,具有重要地位�����。

封裝技術(shù)之演進

? ? ? 晶圓級封裝(WLP)與三維技術(shù)(3 D Technology)是兩種截然不同之技術(shù), 絕不可相混淆���。有許多三維工藝技術(shù) 被應(yīng)用于晶圓級封裝��,但不可歸類于晶圓級封裝���。真正的電子封裝趨勢, 是由二維結(jié)構(gòu)(2D Configuration)進展 到三維工藝技術(shù)(3D Process Technology),然后發(fā)展到三維集成電 路����。

系統(tǒng)級封裝????略

發(fā)展三維整合技術(shù)???

促使三維整合技術(shù)發(fā)展的首要驅(qū)動力����,主要是尺寸的縮小�,也就是使 封裝體盡量縮小到最小體積�。然而, 使用并列封裝(Side by Side)、封裝體 與封裝體之間的堆疊(Stacked Packages)和晶片堆疊(Stacked Die)等方 案��,其導(dǎo)線連接長度仍然太長�。因?qū)?線連接長度太長,則會導(dǎo)致訊號傳輸 速度變慢�����,以及増加電力消耗����。

發(fā)展硅導(dǎo)孔??略

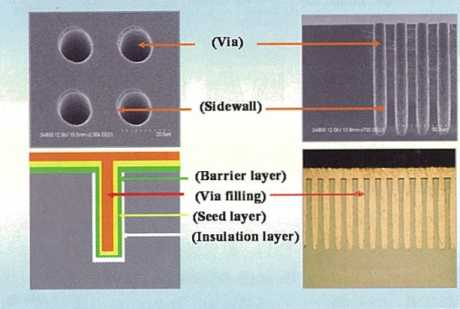

TSV制作3D晶片堆疊 的關(guān)鍵技術(shù)?

?

結(jié)論??略

文章全部詳情,請加華林科納V了解:壹叁叁伍捌零陸肆叁叁叁