隨著集成電路器件的納米化�、高密度化、高集成度及多層金屬互連的進(jìn)步����,半導(dǎo)體技術(shù)節(jié)點(diǎn)越來越先進(jìn),對實(shí)際制造的多個關(guān)鍵環(huán)節(jié)也提出了更多新的要求����。器件特征尺寸的不斷縮小和三維器件結(jié)構(gòu)的日益復(fù)雜性,使得半導(dǎo)體器件對顆粒污染、雜質(zhì)濃度和數(shù)量越來越敏感��。

據(jù)2019年1月28日報道����,臺積電南科14廠發(fā)生一起不合格原料污染事故,預(yù)估損失上萬片晶圓����,受到影響的主要是16/12nm工藝。NVIDIA的GPU芯片�、海思、聯(lián)發(fā)科的手機(jī)芯片以及一些ARM服務(wù)器處理器都使用了這一工藝�,這也是臺積電的主要營收來源之一。臺積電發(fā)生的污染源已被確認(rèn)����,分別為前段刻蝕的鐵離子污染和光刻膠原材料污染。前段晶體管受到污染可能會導(dǎo)致器件發(fā)生不正常的漏電��,進(jìn)而影響產(chǎn)品的良率�����、電學(xué)性能和可靠性��。

2019年2月15日,臺積電坦承�,受到南科14廠污染事件影響,本季營收將減少約5.5億美元���。受到影響的客戶包括輝達(dá)�����、聯(lián)發(fā)科、海思和賽靈思等重量級客戶����,其中輝達(dá)的投片量超過上萬片?����?紤]到此次事故涉及的是相對先進(jìn)的16/12nm工藝��,加上受到影響的股價大跌����,臺積電的實(shí)際損失有可能超過了40億美元。如果再算上事故造成的停機(jī)以及產(chǎn)能和交付上的損失�,則后果將更加慘重。

?

這一事件非常強(qiáng)烈地傳遞了這樣一個信號,隨著集成電路特征尺寸越來越小�����,半導(dǎo)體器件對生產(chǎn)工藝過程中的顆粒��、有機(jī)殘留物����、雜質(zhì)等污染物及濕法清洗的去除能力、缺陷控制��、關(guān)鍵尺寸調(diào)控等的要求越來越高���,同時對工藝化學(xué)品和金屬離子等導(dǎo)致的污染越來越敏感����,使得濕法工藝的關(guān)鍵性和重要性越發(fā)凸顯�����。此外�,芯片制造過程中的每個工藝步驟都有不同的控制和良率要求,特別是先進(jìn)工藝要求制造過程中的顆粒尺寸越來越小�,數(shù)量越來越少�,缺陷密度也越來越低���,這些都增加了工藝復(fù)雜性并帶來越來越多的技術(shù)挑戰(zhàn)��。

技術(shù)節(jié)點(diǎn)演進(jìn)帶來的挑戰(zhàn)

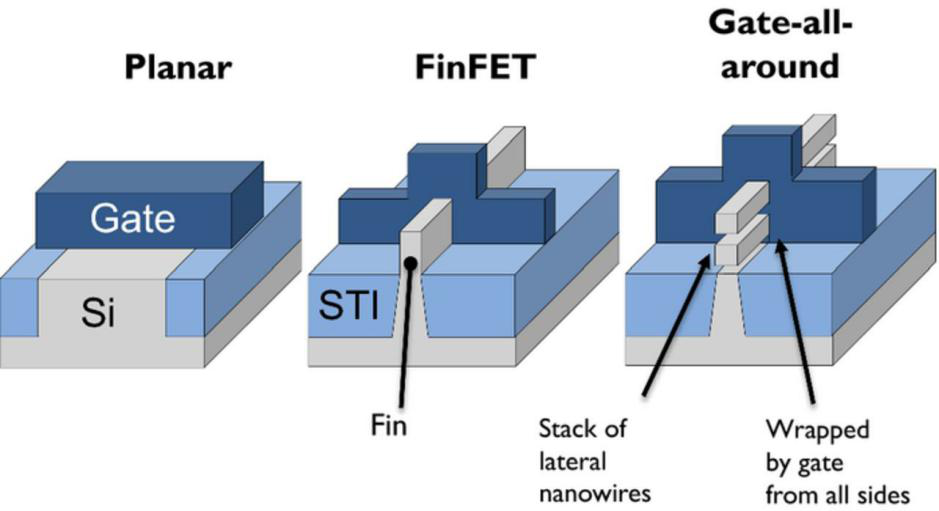

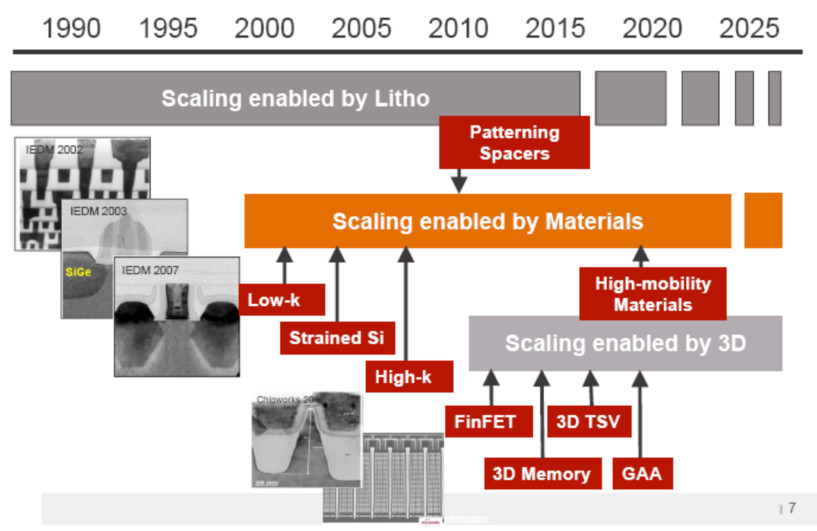

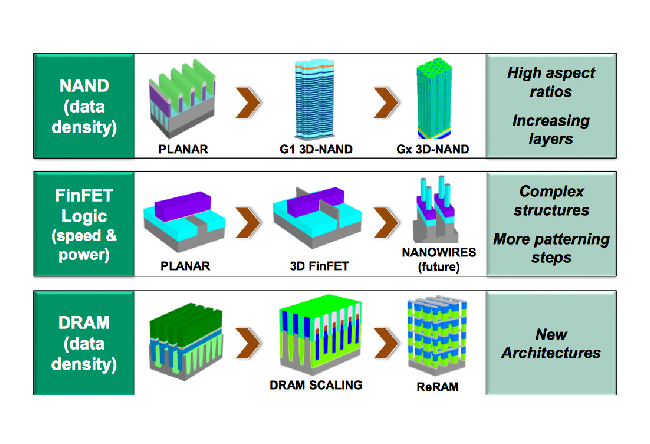

按照摩爾定律��,集成電路器件特征尺寸每兩年縮小0.7倍�����,盡管目前維持這一趨勢所花費(fèi)的時間越來越長��。當(dāng)前,隨著半導(dǎo)體技術(shù)不斷微縮��,先進(jìn)的集成電路器件已從平面向三維結(jié)構(gòu)轉(zhuǎn)變�����,集成電路制造工藝正變得越來越復(fù)雜����,往往需要經(jīng)過幾百甚至上千道的工藝步驟。對于先進(jìn)的半導(dǎo)體器件制造���,每經(jīng)過一道工藝���,硅片表面都會或多或少地存在顆粒污染物����、金屬殘留或有機(jī)物殘留等�,因此幾乎所有工藝步驟都需要濕法處理。對于關(guān)鍵層來說尤其如此��,往往需要經(jīng)過多道清洗或濕法處理步驟��。

?

?

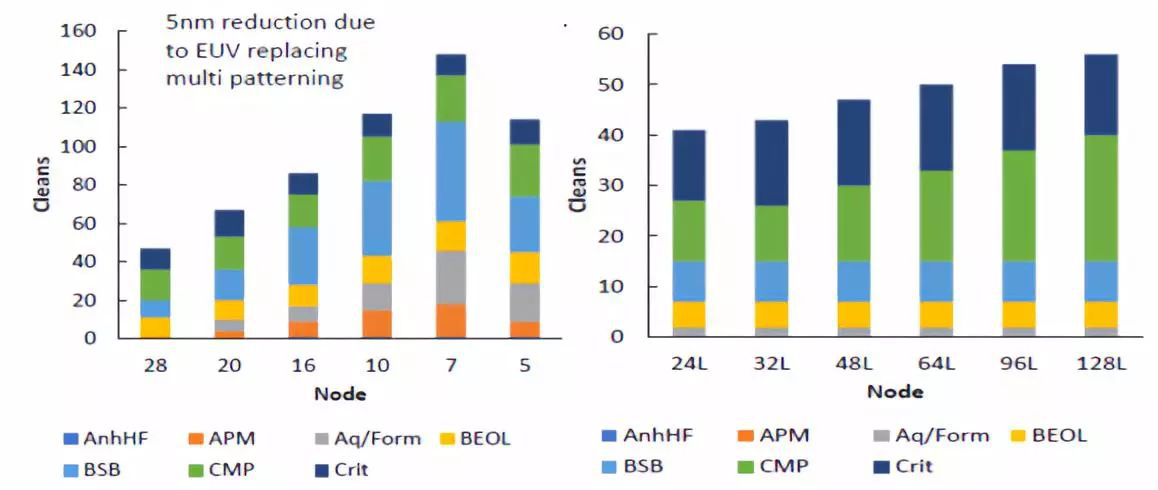

在20nm及以下技術(shù)節(jié)點(diǎn)����,清洗步驟數(shù)量大約占所有工藝步驟數(shù)量的30%,而從16/14nm節(jié)點(diǎn)開始����,更精細(xì)的三維器件結(jié)構(gòu)、更復(fù)雜的前后端工藝集成�、193nm浸入式光刻結(jié)合多重曝光技術(shù)及EUV光刻技術(shù)的引入等多種因素的推動,濕法工藝復(fù)雜性將進(jìn)一步提升����,濕法工藝的步驟也會根據(jù)特定產(chǎn)品的需求而有所增長��。下圖為IC Knowledge LLC 對邏輯器件和3D NAND器件的清洗步驟數(shù)量隨工藝技術(shù)節(jié)點(diǎn)和閃存堆疊層數(shù)而做的調(diào)研數(shù)據(jù)�,可以明顯看到清洗步驟的變化趨勢����,顯示出清洗在先進(jìn)技術(shù)節(jié)點(diǎn)下的重要性和迫切性愈發(fā)增加。

?

對于先進(jìn)技術(shù)節(jié)點(diǎn)�,尤其是10nm、7nm甚至更小的器件����。為了獲得更高的器件可靠性及電學(xué)性能,濕法工藝不僅要能夠從平坦的表面除去更小的隨機(jī)缺陷��、金屬或有機(jī)離子沾污���、特定材料和殘留顆粒等,而且還要能夠適應(yīng)更復(fù)雜���、更精細(xì)的三維器件結(jié)構(gòu)帶來的越來越多的要求���,以免對器件造成不必要的損害或關(guān)鍵材料的損失,從而降低產(chǎn)量和良率���。

表面損傷帶來的挑戰(zhàn)

半導(dǎo)體技術(shù)的不斷演進(jìn)����,促進(jìn)了更多新型材料在先進(jìn)技術(shù)節(jié)點(diǎn)的應(yīng)用,如高K柵介質(zhì)�、金屬柵電極、新的硅化物���、新型低k材料���、新的互連金屬鈷等的引入,對濕法清洗選擇比的要求越來越高����,對前段和后段工藝都會帶來新的挑戰(zhàn)。如何調(diào)控和優(yōu)化濕法處理工藝過程中不同材料間的選擇比����,是一道同時擺在濕法清洗技術(shù)和干法剝離(stripping)技術(shù)面前的難題。

?

對于先進(jìn)技術(shù)節(jié)點(diǎn)下器件的清洗��,一個非常明顯的要求是在去除過程中要避免對圖形造成額外的損傷���。因此�,當(dāng)使用某一類清洗液進(jìn)行處理時就必須了解器件結(jié)構(gòu)上的薄膜材料和組分的構(gòu)成及其比例關(guān)系。比如�,在接觸孔清洗中,為了得到良好的電學(xué)接觸表現(xiàn)�,需要去除接觸孔底部的自然氧化層,但是如果接觸孔氧化物薄膜的密度低于熱生長氧化物�����,則會導(dǎo)致其刻蝕速率非?��??���,圖形形貌及質(zhì)量受到無法預(yù)料的影響��,所以必須保證清洗工藝過程中的選擇比���。再如刻蝕柵電極之后的去膠工藝����、離子注入后的去膠工藝都可能導(dǎo)致大量的硅襯底損失����,尤其是當(dāng)這個過程需要重復(fù)很多遍時,材料的損耗預(yù)計(jì)將更加明顯�,將對器件的電學(xué)性質(zhì)造成顯著的消極影響。

因此��,在半導(dǎo)體前后段制造中�,為了降低材料表面受到的損傷,對材料間的選擇比要求越來越高�����,濕法清洗技術(shù)面臨的挑戰(zhàn)也日益突出���。

高密度三維器件帶來的挑戰(zhàn)

對于平坦的表面來說���,面臨的困難主要集中在化學(xué)清洗方面;而對于三維結(jié)構(gòu)來說����,嚴(yán)密控制材料損失的清洗工藝對于FinFET、3D NAND和其他3D結(jié)構(gòu)至關(guān)重要���,因?yàn)椴磺‘?dāng)?shù)奶幚砜赡軙?dǎo)致圖形損傷���,特別是由于批處理晶圓的非均勻性��,由此帶來非常明顯的器件電學(xué)性能惡化和可靠性問題�。對于這些新型的器件,由于結(jié)構(gòu)本身的復(fù)雜性,使得無損傷并能有效的去除表面顆粒變得非常困難����。對于具有高縱橫比結(jié)構(gòu)的存儲器件來說��,殘留物必須完全去除���,并且不能對結(jié)構(gòu)帶來機(jī)械性損傷或過多的側(cè)壁侵蝕。

?

三維結(jié)構(gòu)的引入��,多種不同種類的材料集成在同樣的系統(tǒng)中���,如何確保在去除顆粒的過程中���,不損傷到器件結(jié)構(gòu)本身,并保持合適的工藝窗口和工藝精度是擺在當(dāng)前半導(dǎo)體集成電路制造過程中的重大難題����。過去經(jīng)常采用的兆頻超聲波攪動這樣的常規(guī)物理清洗方法會對器件結(jié)構(gòu)的損傷和圖形坍塌等有潛在影響��,需要根據(jù)具體的產(chǎn)品特點(diǎn),優(yōu)化���、改進(jìn)或采用更好的處理方式���,以便在保持微粒去除工藝效率的同時不對圖形完整性產(chǎn)生有害影響。

堆疊式圍柵納米線器件提出的挑戰(zhàn)

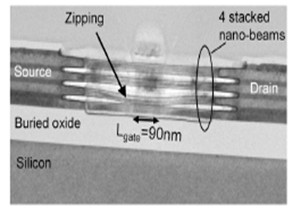

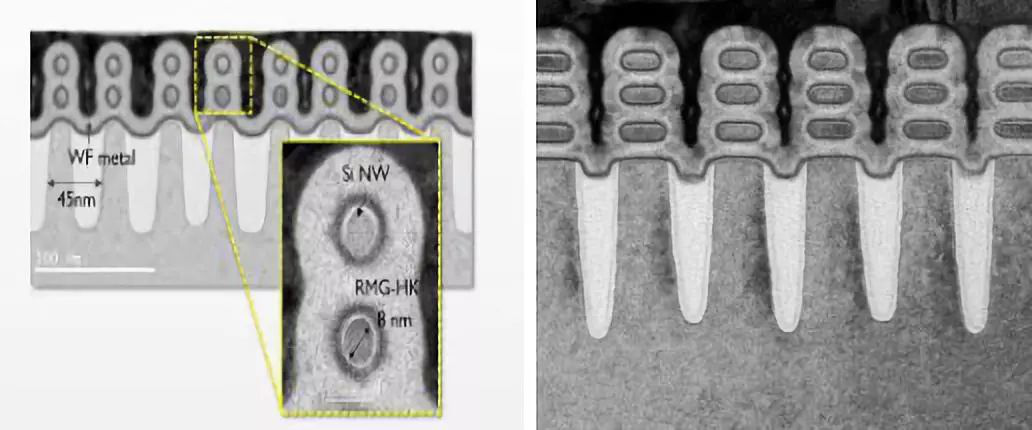

當(dāng)前��,FinFET器件已經(jīng)在22nm節(jié)點(diǎn)開始了應(yīng)用�,有望推進(jìn)到5nm技術(shù)節(jié)點(diǎn)。繼續(xù)向下發(fā)展�����,F(xiàn)inFET器件將遇到更多困難�,而垂直堆疊式圍柵納米線器件由于對短溝道效應(yīng)(SCE)和漏致勢壘效應(yīng)(DIBL)具有天生的免疫性,極好的靜電控制能力����,極高的電流開關(guān)比和縮小尺寸的能力, 已成為集成電路技術(shù)發(fā)展路線圖5nm技術(shù)節(jié)點(diǎn)以下的有力競爭者。

盡管這種器件具有許多突出的優(yōu)點(diǎn)����,可堆疊式圍柵納米線的制備技術(shù)則極具挑戰(zhàn)�����。有報道顯示�,在納米線制備過程中發(fā)現(xiàn)�����,四層結(jié)構(gòu)容易在相鄰納米線間發(fā)生粘連而三層結(jié)構(gòu)則無類似的現(xiàn)象�。這可能是因?yàn)橛捎诓捎昧?/span>SiGe外延工藝,為了避免超晶格中的應(yīng)變弛豫�,Si層間的SiGe的厚度必須被大幅度降低。在采用濕法工藝釋放時�����,溶液中的表面張力很容易誘導(dǎo)相鄰兩層之前納米線的相互粘連�����,導(dǎo)致納米線無法正常釋放����。

為了半導(dǎo)體清洗技術(shù)能滿足不斷出現(xiàn)的新需求,必須根據(jù)產(chǎn)品或具體工藝的技術(shù)特點(diǎn)對現(xiàn)有制造工藝進(jìn)行針對性的調(diào)整和修改���。當(dāng)前�����,堆疊圍柵納米線的制備主要采用后釋放工藝以便與現(xiàn)有的FinFET器件制備技術(shù)有良好的兼容性���,但難點(diǎn)在于如何在納米尺度范圍的柵極溝槽中去除SiGe犧牲層材料。

在這種情況下���,干法清洗技術(shù)逐漸進(jìn)入人們的視野��,而采用HCl氣體去除犧牲層釋放納米線的方法得到了廣泛應(yīng)用���。與傳統(tǒng)濕法清洗技術(shù)不同,這種技術(shù)需要采用新型的干法清洗設(shè)備�����。在SiGe犧牲層去除過程中�,要避免對兩側(cè)SiGe層產(chǎn)生過多的橫向腐蝕,從而影響后續(xù)的柵氧化層和高K金屬柵材料的填充��,這無疑增加了工藝復(fù)雜性和集成難度���。

?

未來與展望

隨著集成電路器件尺寸持續(xù)縮小��,清洗工藝過程中的材料損失和表面粗糙度成為必須關(guān)注的領(lǐng)域����,將微粒去除而又沒有材料損失和圖形損傷是最基本的要求,因此必須考慮周全并有所折衷���。濕法清洗工藝的效果既取決于所采用的濕法工藝化學(xué)品��,還與所采用的設(shè)備密切相關(guān)�。為了推動濕法清洗技術(shù)的快速發(fā)展�����,需要化學(xué)品企業(yè)�����、設(shè)備生產(chǎn)商與芯片制造商緊密協(xié)同���,在技術(shù)上不斷創(chuàng)新��,而合作開發(fā)定制化的化學(xué)品將是未來的重要趨勢���。

另外����,未來干法清洗技術(shù)有望在先進(jìn)器件上得到更廣泛的應(yīng)用���,主要應(yīng)用于對選擇性要求非常高的表面清洗步驟上���,這推動了各種更多創(chuàng)新技術(shù)的研發(fā)����,例如超臨界CO2(Super Critical CO2)清洗。

多年來得到廣泛應(yīng)用的各種商用清洗技術(shù)是解決當(dāng)前所面臨的一切挑戰(zhàn)的基礎(chǔ)���,而各種新材料���、新技術(shù)、器件和新結(jié)構(gòu)等的大量出現(xiàn)必將推動半導(dǎo)體清洗技術(shù)的快速發(fā)展����,并持續(xù)滿足半導(dǎo)體集成電路制造提出的越來越嚴(yán)苛的技術(shù)需求。

免責(zé)聲明:文章來源于網(wǎng)絡(luò)����,如有侵權(quán)請聯(lián)系作者刪除�����。