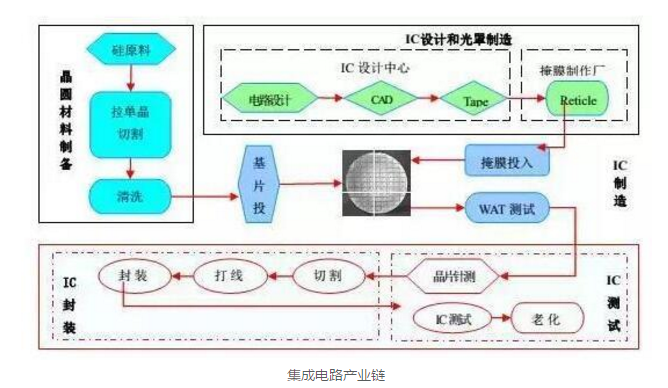

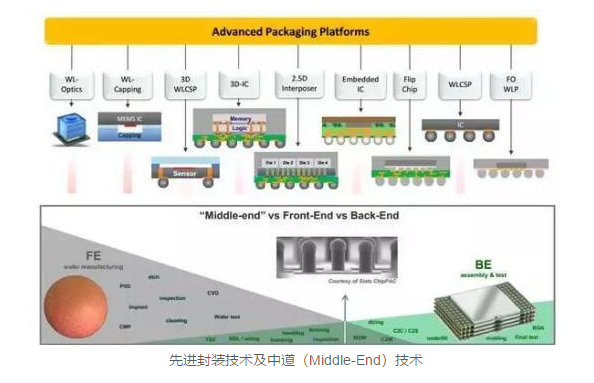

半導(dǎo)體產(chǎn)品的加工過程主要包括晶圓制造(前道�����,Front-End)和封裝(后道����,Back-End)測(cè)試����,隨著先進(jìn)封裝技術(shù)的滲透�,出現(xiàn)介于晶圓制造和封裝之間的加工環(huán)節(jié),稱為中道(Middle-End)�����。由于半導(dǎo)體產(chǎn)品的加工工序多�����,所以在制造過程中需要大量的半導(dǎo)體設(shè)備和材料�。

一、晶圓制造

在這里���,我們以最為復(fù)雜的晶圓制造(前道)和傳統(tǒng)封裝(后道)工藝為例��,說明制造過程的所需要的設(shè)備和材料��。

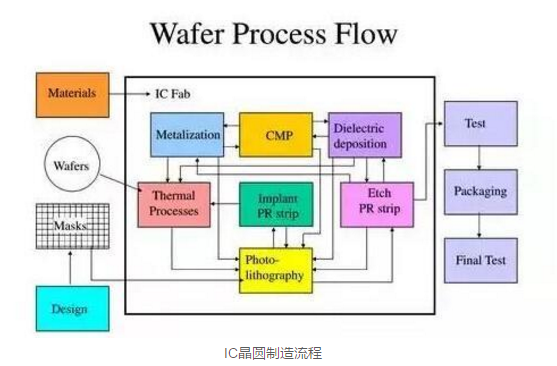

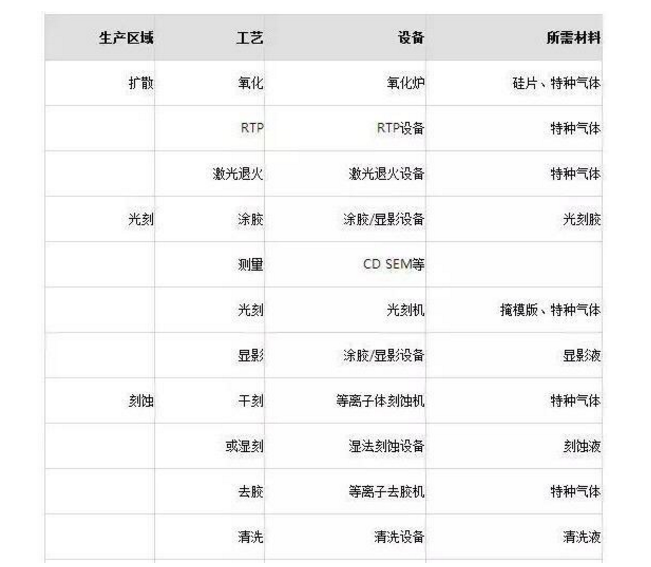

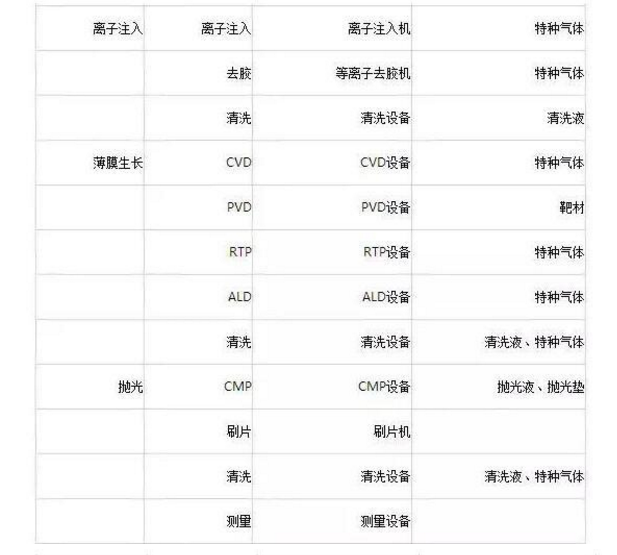

晶圓生產(chǎn)線可以分成7個(gè)獨(dú)立的生產(chǎn)區(qū)域:擴(kuò)散(Thermal Process)�����、光刻(Photo- lithography)�����、刻蝕(Etch)���、離子注入(Ion Implant)��、薄膜生長(zhǎng)(Dielectric Deposition)�、拋光(CMP)���、金屬化(Metalization)��。這7個(gè)主要的生產(chǎn)區(qū)和相關(guān)步驟以及測(cè)量等都是晶圓潔凈廠房進(jìn)行的���。在這幾個(gè)生產(chǎn)區(qū)都放置有若干種半導(dǎo)體設(shè)備�,滿足不同的需要。例如在光刻區(qū)�����,除了光刻機(jī)之外����,還會(huì)有配套的涂膠/顯影和測(cè)量設(shè)備�����。

二�、封裝

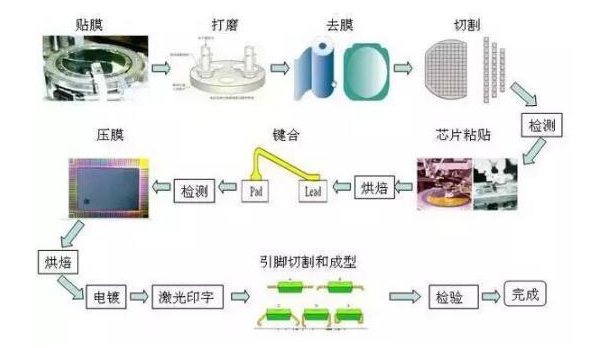

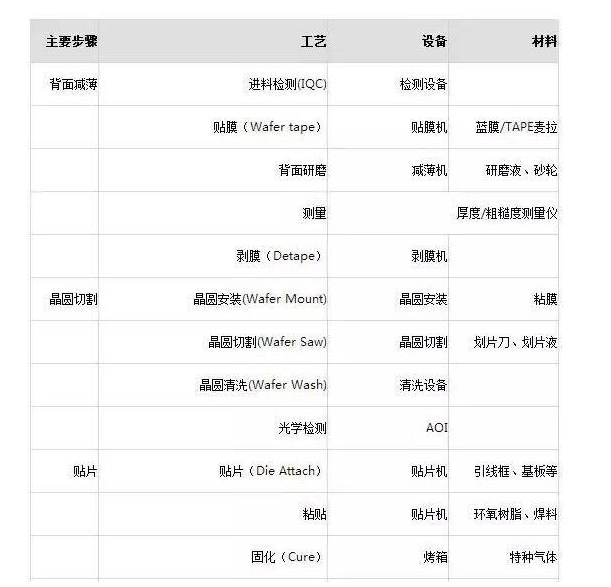

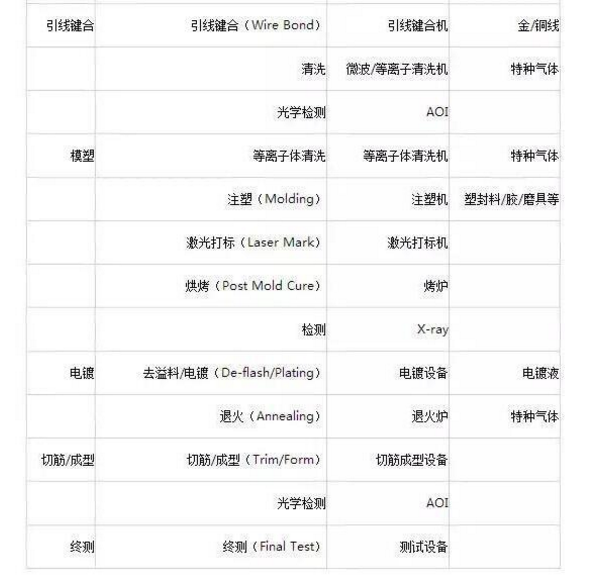

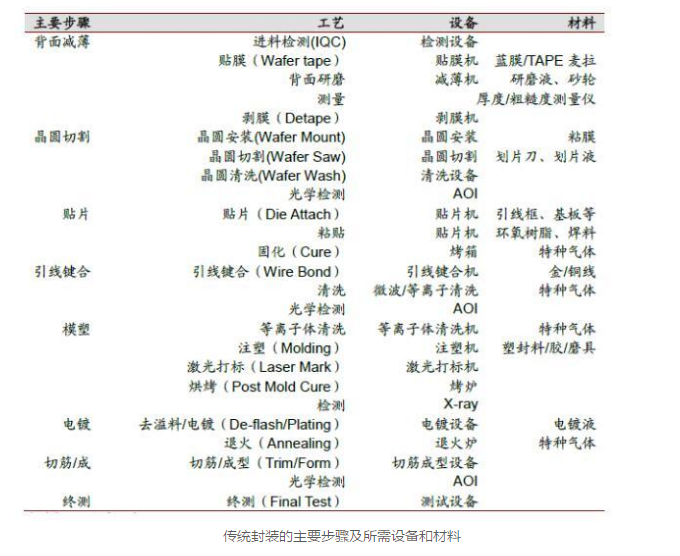

傳統(tǒng)封裝(后道)測(cè)試工藝可以大致分為背面減薄�����、晶圓切割�����、貼片��、引線鍵合���、模塑�����、電鍍�����、切筋/成型和終測(cè)等8個(gè)主要步驟�。與IC晶圓制造(前道)相比,后道封裝相對(duì)簡(jiǎn)單��,技術(shù)難度較低���,對(duì)工藝環(huán)境����、設(shè)備和材料的要求遠(yuǎn)低于晶圓制造����。

三、半導(dǎo)體工藝解析

半導(dǎo)體制造工藝是集成電路實(shí)現(xiàn)的手段��,也是集成電路設(shè)計(jì)的基礎(chǔ)��。自從1948年晶體管發(fā)明以來�����,半導(dǎo)體器件工藝技術(shù)的發(fā)展經(jīng)歷了三個(gè)主要階段:1950年采用合金法工藝����,第一次生產(chǎn)出了實(shí)用化的合金結(jié)三極管;1955年擴(kuò)散技術(shù)的采用是半導(dǎo)體器件制造技術(shù)的重大發(fā)展�,為制造高頻器件開辟了新途徑;1960年平面工藝和外延技術(shù)的出現(xiàn)是半導(dǎo)體制造技術(shù)的重大變革����,不但大幅度地提高了器件的頻率、功率特性�����,改善了器件的穩(wěn)定性和可靠性��,而且也使半導(dǎo)體集成電路的工業(yè)化批量生產(chǎn)得以成為現(xiàn)實(shí)��。目前平面工藝仍然是半導(dǎo)體器件和集成電路生產(chǎn)的主流工藝��。

在半導(dǎo)體制造工藝發(fā)展的前35年�����,特征尺寸的縮小是半導(dǎo)體技術(shù)發(fā)展的一個(gè)標(biāo)志��,有效等比縮?��。⊿caling-down)的努力重點(diǎn)集中在通過提高器件速度以及在成品率可接受的芯片上集成更多的器件和功能來提高性能���。然而���,當(dāng)半導(dǎo)體行業(yè)演進(jìn)到45nm節(jié)點(diǎn)或更小尺寸的時(shí)候,器件的等比縮小將引發(fā)巨大的技術(shù)挑戰(zhàn)���。其中兩大挑戰(zhàn)是不斷增長(zhǎng)的靜態(tài)功耗和器件特性的不一致性��。這些問題來源于CMOS工藝快要到達(dá)原子理論和量子力學(xué)所決定的物理極限��。

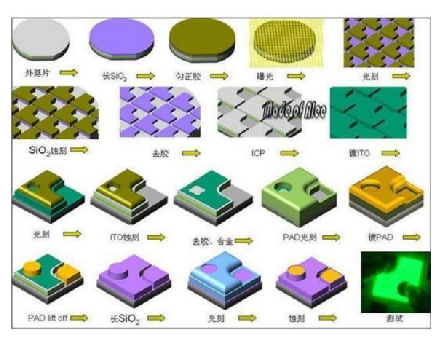

集成電路制造就是在硅片上執(zhí)行一系列復(fù)雜的化學(xué)或者物理操作�����,簡(jiǎn)單講�����,這些操作可以分為四大基本類:薄膜制作(1ayer)��、刻?�。╬attern)�、刻蝕和摻雜。這些在單個(gè)芯片上制作晶體管和加工互連線的技術(shù)綜合起來就成為半導(dǎo)體制造工藝���。

1、光刻工藝

光刻是通過一系列生產(chǎn)步驟將晶圓表面薄膜的特定部分除去的工藝��。在此之后�����,晶圓表面會(huì)留下帶有微圖形結(jié)構(gòu)的薄膜����。被除去的部分可能形狀是薄膜內(nèi)的孔或是殘留的島狀部分。光刻生產(chǎn)的目標(biāo)是根據(jù)電路設(shè)計(jì)的要求���,生成尺寸精確的特征圖形�����,且在晶圓表面的位置要正確��,而且與其他部件的關(guān)聯(lián)也正確��。通過光刻過程����,最終在晶圓片上保留特征圖形的部分。有時(shí)光刻工藝又被稱為Photomasking�, Masking,Photolithography或Microlithography�����,是半導(dǎo)體制造工藝中最關(guān)鍵的�����。在光刻過程中產(chǎn)生的錯(cuò)誤可造成圖形歪曲或套準(zhǔn)不好����,最終可轉(zhuǎn)化為對(duì)器件的電特性產(chǎn)生影響

主要設(shè)備廠商:ASML、尼康�����、佳能�、上海微電子裝備SMEE

2、摻雜工藝

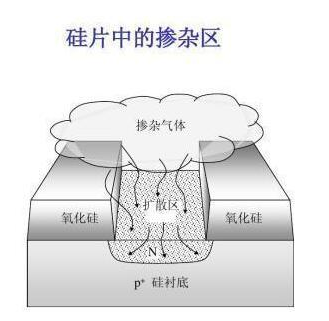

摻雜是將特定量的雜質(zhì)通過薄膜開口引入晶圓表層的工藝過程���,它有兩種實(shí)現(xiàn)方法:熱擴(kuò)散(thermal diffusion)和離子注入(implantation)�。熱擴(kuò)散是在1000℃左右高溫下發(fā)生的化學(xué)反應(yīng),晶圓暴露在一定摻雜元素氣態(tài)下�。擴(kuò)散的簡(jiǎn)單例子就如同除臭劑從壓力容器內(nèi)釋放到房間內(nèi)。氣態(tài)下的摻雜原子通過擴(kuò)散化學(xué)反應(yīng)遷移到暴露的晶圓表面�����,形成一層薄膜��,在芯片應(yīng)用中����,熱擴(kuò)散也稱為固態(tài)擴(kuò)散����,因?yàn)榫A材料是固態(tài)的。熱擴(kuò)散是一個(gè)化學(xué)反應(yīng)過程���。而離子注入是一個(gè)物理反應(yīng)過程�。晶圓被放在離子注入機(jī)的一端�����,摻雜離子源(通常為氣態(tài))在另一端���。在離子源一端��,摻雜體原子被離子化(帶有一定的電荷)���,被電場(chǎng)加到超高速�����,穿過晶圓表層����。原子的動(dòng)量將摻雜原子注入晶圓表層�����,就好像一粒子彈從槍內(nèi)射入墻中����。摻雜工藝的目的是在晶圓表層內(nèi)建立兜形區(qū),或是富含電子(N型)或是富含空穴(P型)�。這些兜形區(qū)形成電性活躍區(qū)的PN結(jié),在電路中的晶體管����、二極管��、電容器����、電阻器都依靠它來工作�����。

3��、薄膜生產(chǎn)工藝

在晶圓表面生成了許多的薄膜�,這些薄膜可以是絕緣體�、半導(dǎo)體或?qū)w。它們由不同的材料組成����,是使用多種工藝生長(zhǎng)或淀積的。這些主要的工藝技術(shù)是生長(zhǎng)二氧化硅膜和淀積不同材料的薄膜���。通用的淀積技術(shù)是化學(xué)氣相淀積(CVD)��、蒸發(fā)和濺射���。

4��、熱處理工藝

熱處理是簡(jiǎn)單地將晶圓加熱和冷卻來達(dá)到特定結(jié)果的工藝�。在熱處理的過程中���,晶圓上沒有增加或減去任何物質(zhì)�����,另外會(huì)有一些污染物和水汽從晶圓上蒸發(fā)��。在離子注入工藝后會(huì)有一步重要的熱處理�����。摻雜原子的注入所造成的晶圓損傷會(huì)被熱處理修復(fù)���,這稱為退火,溫度一般在1000℃左右����。另外,金屬導(dǎo)線在晶圓上制成后會(huì)有一步熱處理����。這些導(dǎo)線在電路的各個(gè)器件之間承載電流���。為了確保良好的導(dǎo)電性,金屬會(huì)在450℃熱處理后與晶圓表面緊密熔合����。熱處理的第三種用途是通過加熱在晶圓表面的光刻膠將溶劑蒸發(fā)掉,從而得到精確的圖形����。免責(zé)聲明:文章來源于網(wǎng)絡(luò),如有侵權(quán)請(qǐng)聯(lián)系作者刪除��。